Проектирование электронных модулей с использованием САПР Cadence Allegro / OrCAD PCB Editor. 3 дня, Москва

- Цель – изучение базовых и расширенных приёмов работы с программой Allegro / OrCAD PCB Editor

- Категории слушателей – конструкторы печатных плат

- Срок обучения — 24 часа, с включением практических занятий

- Форма обучения – очная, с отрывом от производства

- Режим занятий — 8 часов ежедневно

- Формат занятий – тренинг, с выдачей сертификатов.

Стоимость

Стоимость в расчете на 1 чел. зависит от размера группы и других факторов. Уточняйте цену при подаче заявки.

| Раздел I. Введение | |

| 1.1 | Структура программного обеспечения Cadence Allegro PCB Designer. Особенности учебного курса и его ключевые темы. |

| 1.2 | Справочная система Cadence Help: структура и особенности. Справочные ресурсы интернет. Портал support.cadence.com. Техническая поддержка. |

| Раздел II. Схемный редактор OrCAD Capture. | |

| 2.1 | Основные настройки схемотехнического редактора. Объяснение логики работы с сеткой в OrCAD Capture. |

| 2.2 | Структура проекта схемы. Подключение библиотек различных объектов, используемых на ПП. Design Cache. Понятие Flat Design и иерархического проекта. |

| 2.3 | Создание пользовательской библиотеки. Создание рамки схемного листа. Рисование простейшего 2-х пинового резистора. |

| 2.4 | Знакомство с инструментами рисования графических примитивов. Расставление пинов компонента и назначение свойств пинам. Понятие альтернативного вида схемного элемента. |

| 2.5 | Введение понятия гомогенные и гетерогенные компоненты. Рисование простейшего гомогенного компонента: резисторной сборки. Задание правил обмена пинов посекционно между одинаковыми секциями. |

| 2.6 | Рисование гетерогенного компонента. Инструмент View package -> Edit properties, как средство табличного задания правил сваппирования пинов внутри одной секции. |

| 2.7 | Введение понятия локальный объект/глобальный объект. Объяснение правил использования “Power pin”. Знакомство с другими глобальными объектами в схеме: Power/Ground symbol, Off page connector, port. |

| 2.8 | Создание иерархического проекта. Понятие простой/сложный иерархический проект. |

| 2.9 | Объединение индексируемых сигналов в шину “Bus group”. Рисование шины, правила задания имени шины. Объединение неиндексируемых сигналов в группу “Net group”. Рисование группы сигналов, правила задания имени группы и соединения одноименной группы на различных листах схемы. |

| 2.10 | Проверка схемы на наличие ошибок. Инструменты проверки. Сравнение 2-х схем друг с другом. Формирование отчётов. |

| 2.11 | Получение Netlist из готовой схемы. Настройка конфигурационного файла для получения Netlist. Замена свойств компонентов по умолчанию пользовательскими. |

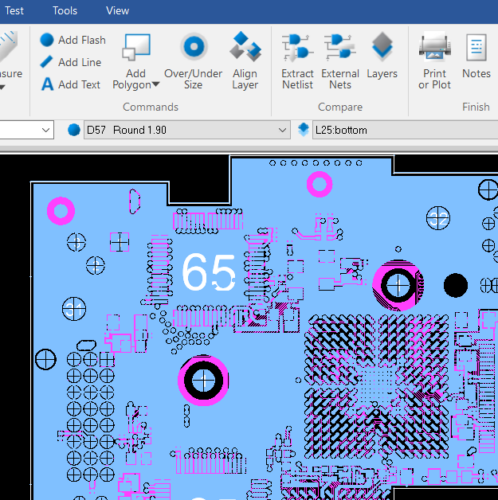

| Раздел III. Управление рабочей средой Allegro PCB Editor | |

| 3.1 | Структура классов и подклассов (слоев). Контроль цвета и видимости слоев. Панель Visibility. Теневой режим. Параметрические файлы |

| 3.2 | Панель Find. Фильтр объектов при выделении. Поиск объектов. Предварительное выделение. Команды правой кнопки мыши. |

| 3.3 | Режимы работы редактора. Просмотр свойств объектов топологии. Измерение расстояния. |

| Раздел IV. Создание падстеков | |

| 4.1 | Типовая структура падстека. |

| 4.2 | Работа в Pad Designer. Создание планарного вывода и сквозного. |

| 4.3 | Создание КП произвольной формы при помощи объектов Shape. |

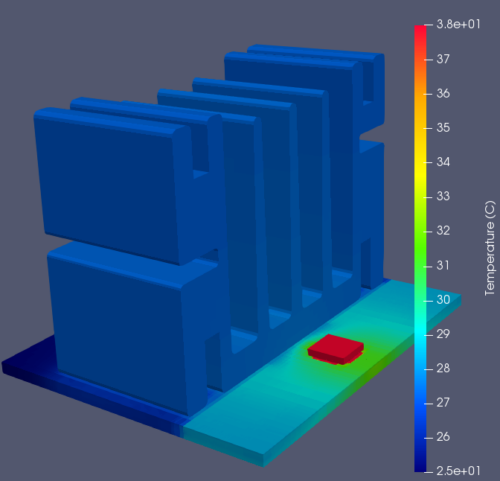

| 4.4 | Идеология создания теплосъёмных КП и расположения на них отверстий. Выгоды отверстия на КП, как отдельного объекта. |

| Раздел V. Создание символа посадочного места | |

| 5.1 | Типы символов. Настройка путей поиска посадочных мест, STEP моделей и д.р. необходимых файлов. |

| 5.2 | Инструменты рисования. Создание символа ручным полуавтоматическим способом: настройка параметров дизайна, установка начала координат, размещение выводов, автонумерация выводов, размещение рисунка сборки и шелкографии, размещение технологических зон. |

| 5.3 | Общее знакомство пользователя с процессом подключения STEP моделей к посадочным местам компонентов. |

| 5.4 | Общая информация об OrCAD Library Builder – инструменту для создания символов посадочных мест. |

| Раздел VI.Создание механических символов | |

| 6.1 | Понятие механического символа. Ввод контура платы. Фаски и скругления. |

| 6.2 | Размещение крепежных отверстий. |

| 6.3 | Простановка размеров. |

| Раздел VII. Импорт данных из схемы | |

| 7.1 | Маршрут передачи данных. Файлы списка цепей и компонентов (pst*.dat). |

| Раздел VIII. Система ограничений (DRC) | |

| 8.1 | Концепция интерактивной трассировки под управлением ограничений. Типы ограничений. |

| 8.2 | Constraint Manager: интерфейс пользователя. |

| 8.3 | Физические ограничения: набор ограничений (PCSet), ввод значений, настройка переходных отверстий, создание класса цепей, назначений правил напрямую цепям |

| 8.4 | Пространственные ограничения (правила зазоров): набор ограничений (SCSet), ввод значений, создание класса цепей, назначение SCSet для класса цепей, правила зазоров между классами цепей |

| 8.5 | Контроль физических и пространственных правил. Отображение маркеров ошибок. |

| 8.6 | Создание регионов ограничений. Правила регионов. Копирование регионов. |

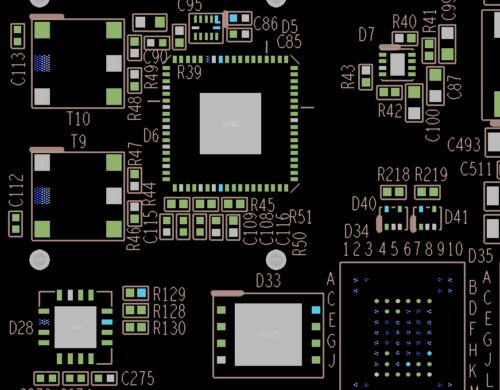

| Раздел IX. Размещение компонентов | |

| 9.1 | Способы размещения: ручной, быстрый и автоматический. Размещение компонентов по схеме. |

| 9.2 | Стратегия размещения. Компоновка при помощи комнат. Создание комнат. Подключение к логике предварительно размещенных компонентов. |

| 9.3 | Свойства размещения. Режим размещения. Выравнивание компонентов. Перекрестное выделение между схемой и платой. |

| 9.4 | Создание модуля повторного размещения. Удаление компонентов. |

| 9.5 | Управление линиями связей |

| 9.6 | Обновление посадочных мест из библиотек, обновление и редактирование выводов компонентов. Создание библиотеки компонентов из платы. |

| Раздел X. Трассировка | |

| 10.1 | Сетка трассировки. Настройка параметров интерактивной трассировки по умолчанию. |

| 10.2 | Управление интерактивной трассировкой с помощью панели Options. |

| 10.3 | Редактирование трассировки: удаление, слайдинг, изменение ширины трасс |

| 10.4 | Создание фэнаутов. Копирование фэнаутов. |

| Раздел XI. Работа с полигонами | |

| 11.1 | Меню Shape. Понятие статических и динамических полигонов. |

| 11.2 | Рисование полигонов. Редактирование полигонов. Заливка полигонов. Индивидуальные свойства полигонов. Термальные барьеры. Зазоры. |

| Раздел XII. Подготовка к постпроцессам | |

| 12.1 | Перенумерация компонентов. Свапирование. Передача данных на схему. |

| Раздел XIII. Подготовка к производству | |

| 13.1 | Формирование слоя шелкографии |

| 13.2 | Генерация отчетов. Подготовка формы отчета. |

| 13.3 | Просмотр статистики проекта. Проверка ошибок. Скрытие маркеров ошибок. |

| 13.4 | Настройка гербер-файлов. Генерация гербер-файлов. Просмотр. |

| 13.5 | Подготовка и генерация файлов сверловки. Настройка и размещение таблицы сверловки. |

| 13.6 | Формирование Pick’n’Place файла. |

| Раздел XIV. Основы работы с электрическими ограничениями | |

| 14.1 | Понятие электрических (высокоскоростных ограничений). Обзор электрических ограничений |

| 14.2 | Работа с дифференциальными парами |

| 14.3 | Контроль задержки сигналов |

| 14.4 | Понятие виртуальных пинов “T-точки”. Организация групп сигналов. Применение виртуальных пинов для сравнения длин различных участков трассировки. |

| 14.5 | Обзор опций High-Speed, Design Planning. |